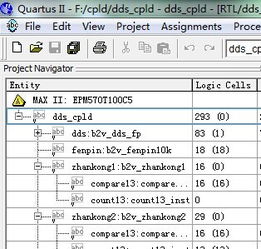

quartus多个模块,Quarus II中多个模块的设计与连接

时间:2024-09-14 来源:网络 人气:

Quarus II中多个模块的设计与连接

在FPGA(现场可编程门阵列)设计中,Quarus II是业界广泛使用的开发工具之一。它提供了强大的功能,使得设计者能够轻松地创建、编译和仿真复杂的数字系统。在Quarus II中,设计通常被分解为多个模块,以便于管理和维护。本文将详细介绍如何在Quarus II中设计多个模块,并探讨它们之间的连接方法。

标签:模块设计

一、模块设计的基本概念

在FPGA设计中,模块是基本的设计单元。每个模块通常负责特定的功能,如计数器、寄存器、算术运算等。模块设计的关键在于定义模块的输入和输出端口,以及模块内部的逻辑。

标签:模块类型

二、常见的模块类型

在Quarus II中,常见的模块类型包括:

组合逻辑模块:处理输入信号并产生输出信号,不包含任何存储元素。

时序逻辑模块:包含存储元素,如寄存器,用于存储状态信息。

存储器模块:用于存储大量数据,如RAM或ROM。

标签:模块设计步骤

三、模块设计步骤

以下是模块设计的基本步骤:

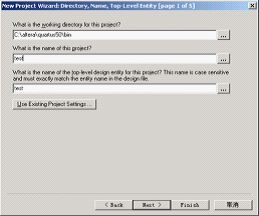

定义模块的功能和性能要求。

设计模块的内部结构,包括逻辑单元和存储元素。

定义模块的输入和输出端口。

编写模块的Verilog或VHDL代码。

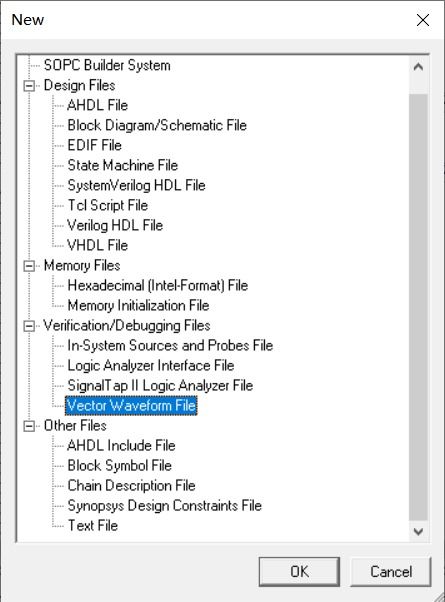

对模块进行仿真,验证其功能。

标签:模块连接

四、模块之间的连接方法

在Quarus II中,模块之间的连接可以通过以下几种方式实现:

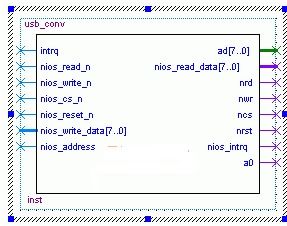

原理图连接:通过原理图编辑器将模块的输入和输出端口连接起来。

HDL代码连接:在Verilog或VHDL代码中,使用实例化语句将模块连接起来。

IP核连接:使用Quarus II提供的IP核库中的模块,通过配置参数进行连接。

标签:原理图连接

五、原理图连接方法

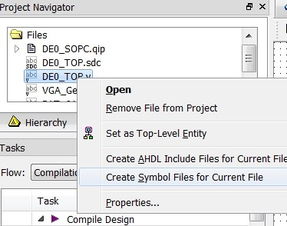

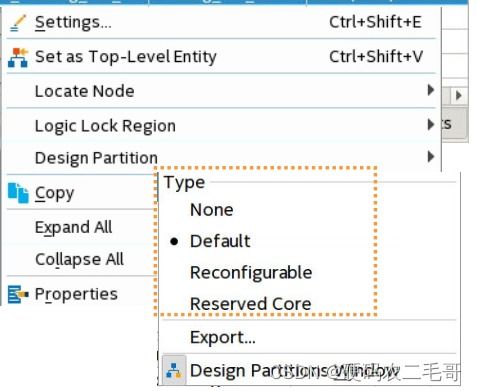

原理图连接是Quarus II中最直观的连接方式。以下是原理图连接的基本步骤:

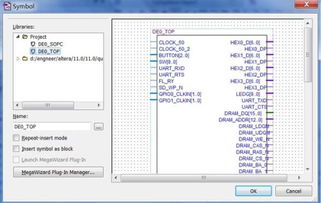

打开原理图编辑器。

从库中拖拽所需模块到原理图编辑器。

连接模块的输入和输出端口。

保存并编译原理图。

标签:HDL代码连接

六、HDL代码连接方法

HDL代码连接是通过编写Verilog或VHDL代码来实现模块之间的连接。以下是HDL代码连接的基本步骤:

编写Verilog或VHDL代码,定义模块的输入和输出端口。

使用实例化语句将模块连接起来。

编写模块之间的逻辑关系。

保存并编译代码。

标签:IP核连接

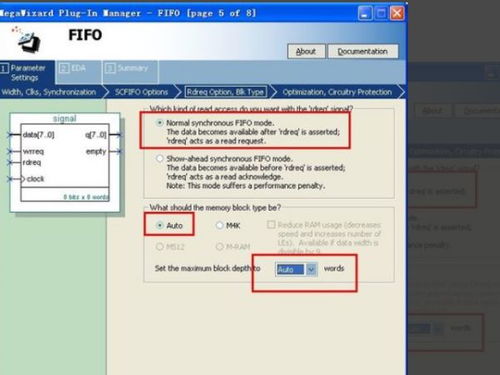

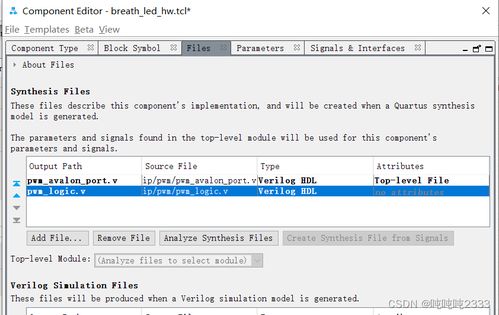

七、IP核连接方法

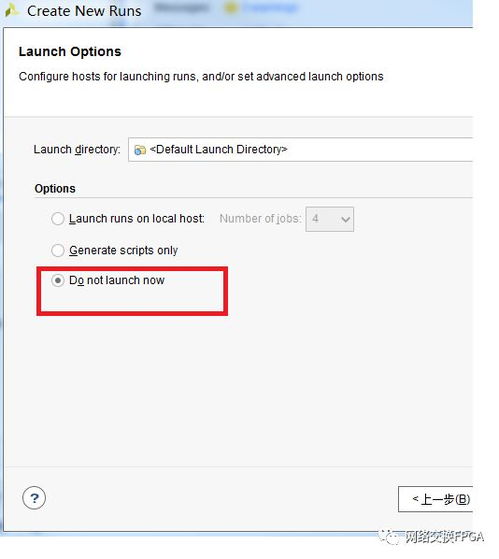

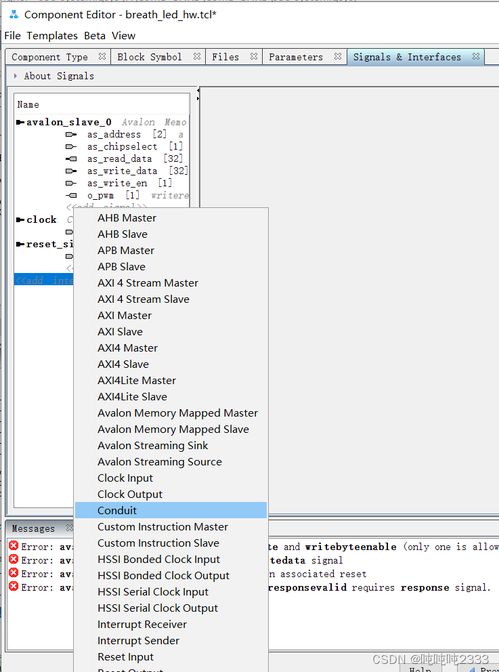

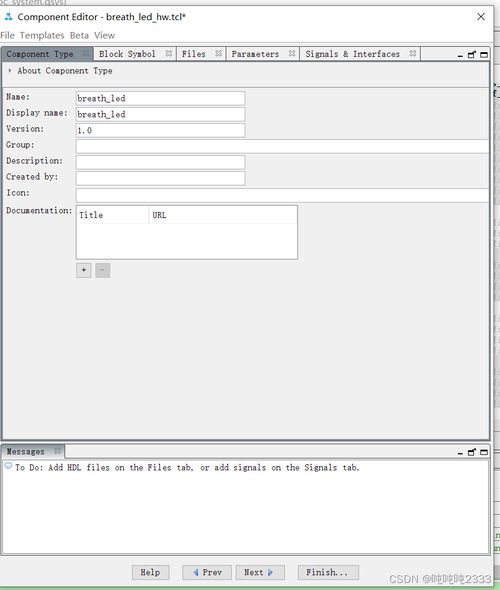

IP核是Quarus II提供的预定义模块,可以快速集成到设计中。以下是IP核连接的基本步骤:

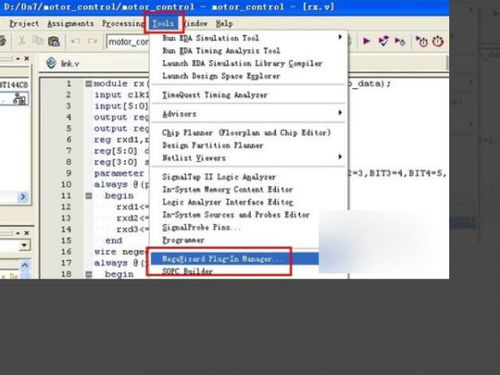

在Quarus II中打开IP核库。

选择所需的IP核,并配置其参数。

将IP核添加到设计中。

连接IP核的输入和输出端口。

保存并编译设计。

标签:总结

八、总结

在Quarus II中,设计多个模块并连接它们是FPGA设计的基本技能。通过本文的介绍,读者可以了解到模块设计的基本概念、常见模块类型、设计步骤以及模块之间的连接方法。掌握这些技能对于FPGA设计者来说至关重要,有助于提高设计效率和系统性能。

相关推荐

教程资讯

教程资讯排行