并行crc算法硬件实现研究与vhdl设计,crc并行计算原理

时间:2024-09-12 来源:网络 人气:

并行crc算法硬件实现研究与vhdl设计目录

并行crc算法硬件实现研究与vhdl设计

这是序言。

随着信息技术的飞速发展,数据传输的可靠性和速率已成为衡量通信系统性能的重要指标。循环冗余校验(CRC)算法作为一种高效的纠错机制,在数据传输中发挥着重要的作用。本文旨在探讨并行CRC算法的硬件实现,并使用VHDL语言设计以提高CRC算法的运行效率。

并行CRC算法

并行CRC算法是将传统的串行CRC算法并行化的方法。通过将数据分成多段,并行计算每段的CRC值来提高算法的运行速度。与传统的串行CRC算法相比,并行CRC算法在保证数据传输可靠性的同时,显著提高了数据处理效率。

并行CRC算法的硬件实现。

并行CRC算法的硬件实现主要包括以下步骤:

数据预处理:将输入数据分成多个部分并行计算。并行计算:对拆分后的数据进行并行计算,求出各段的CRC值。合并结果:合并各部分的CRC值,得到最终的CRC值。基于VHDL的并行CRC算法。

本文采用VHDL语言设计并行CRC算法,主要分为以下模块:

数据预处理模块:将输入数据分成多个部分,准备并行计算。并行计算模块:对拆分后的数据进行并行计算,得到每段的CRC值。结果合并模块:合并各部分的CRC值,得到最终的CRC值。控制模块:协调各模块的运行,确保整个系统的正常运行。模拟和验证。

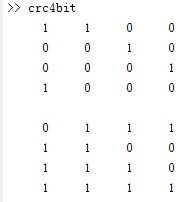

为了验证所设计的并行CRC算法的准确性和性能,本文使用ModelSim仿真工具对VHDL代码进行仿真。模拟结果显示,所设计的并行CRC算法能够正确计算输入数据的CRC值,运行效率高。

来分析实验结果。

本文主要从以下角度对所设计的并行CRC算法进行了实验分析。

运行效率:比较串行CRC算法和并行CRC算法的运行时间,验证并行CRC算法的运行效率。资源消耗:分析并行CRC算法的硬件资源消耗,如逻辑资源、存储资源等。可靠性:验证并行CRC算法在数据传输中的错误检测能力。结论。

本论文研究并行CRC算法的硬件实现,用VHDL语言设计。模拟结果显示,所设计的并行CRC算法能够正确计算输入数据的CRC值,运行效率高。本文的研究结果为并行CRC算法在通信系统中的应用提供了参考。

标签。

关键词:并行CRC算法;是VHDL;硬件实现,数据传输;错误检测。

crc并行计算原理

3CRC并行计算原理详解

CRC(循环冗余校验)是在数据通信和存储中广泛使用的错误检测技术。随着数据传输速度的提高和复杂性的增加,传统的串行CRC计算方法已经不能满足高速数据通信的需要。于是出现了并行计算CRC技术,在此详细介绍CRC并行计算的原理。

标准:CRC简介

CRC(循环冗余校验码)是一种基于多项式除法的校验方法。通过在数据帧的最后添加校验码,整个数据帧可以被特定的多项式整除。在接收端,用同样的方法检查数据的帧,如果能够除尽,就表示发送过程中没有发生错误。

3标签:串行CRC计算。

传统的串行CRC计算方法是以位为单位计算数据的,可以应对数据传输速率较低的情况。在高速数据通信中,串行方式会导致计算速度变慢,无法支持实时性。于是,并行计算CRC技术登场了。

3标签:并行CRC计算原理

并行CRC计算是指将数据分割成多个部分同时进行计算。具体来说,就是将数据帧分割成多个字节,每个字节对应一个运算单元。每个计算单元独立进行CRC计算,然后将计算结果合并,得到最终的CRC校验码。

3标签:并行计算的优势。

与串行CRC相比,并行CRC有以下优点:

提高计算速度:并行计算可以同时处理多个数据单元,因此计算速度大幅提高。降低延迟:并行计算减少了数据传输的延迟,提高了系统的实时性。减少资源消耗:并行计算减少了计算单元的数量,减少了硬件消耗。3标签:并行CRC计算方法。

并行CRC计算主要有以下几种方法。

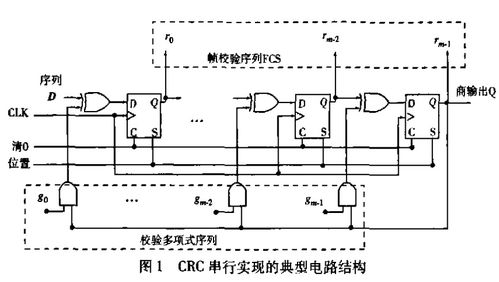

LFSR(线性反馈移位寄存器)的并行计算方法:LFSR是一种常用的CRC计算方法,通过对数据和LFSR的输出进行异或操作来实现CRC计算。基于查找表的并行计算法:查找表法是一种常用的并行CRC算法,通过预先计算并存储所有可能的CRC值,实现快速查找和计算。基于FPGA(现场可编程门阵列)的并行计算方法:FPGA是一种可编程硬件平台,可用于实现具有灵活性和可伸缩性的并行CRC计算。3标签:并行CRC计算的应用

并行CRC计算在以下领域被广泛使用。

高速数据通信:以太网、无线通信等。存储系统:硬盘、固态硬盘等。嵌入式系统:单机、嵌入式处理器等。3标签:总结

并行CRC计算技术是提高数据通信和存储系统可靠性的重要手段。通过并行计算,可以显著提高CRC的计算速度,降低延迟,减少资源消耗。随着技术的不断发展,并行CRC计算被应用于更多的领域,为数据传输和存储提供更加可靠的安全保障。

crc并行公式推导

CRC并行公式的推导研究3序章

循环冗余校验(CRC)是一种广泛应用于数据传输和保存的校验技术,它可以有效地检测出数据传输过程中可能出现的错误。传统的CRC检查一般采用串行算法,但是随着数据传输速度的提高,串行算法的效率已经跟不上了。因此,并行CRC算法的研究和应用越来越受到重视。本论文的目的是,导出CRC的并行式,分析性能特性。

3CRC的基本原理

CRC是基于多项式除法的检验技术。在CRC校验过程中,发送方将数据除以一个生成多项式和2模,得到的余数作为校验码附在数据后面发送。收信方对收到的数据进行同模2除法,余数为0,则认为数据传输正确;如果不是,就判断数据传送有错误。

3CRC串行算法。

CRC串行算法一般使用移位寄存器和异或运算来实现。在串行算法中,数据位依次通过移位寄存器,与生成多项式进行异或运算。每处理一位数据,移位寄存器中的数据就向右移动一位,产生的多项式的最高位与移位寄存器的低位进行异或运算。

3CRC并行算法。

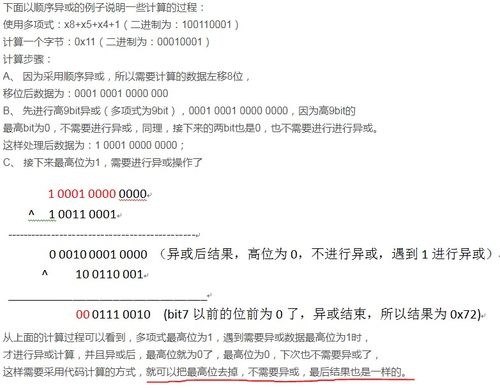

CRC并行算法以提高CRC检查的效率为目标,通过并行处理数据位来缩短检查时间。这里主要基于查找表法导出CRC并列式。

3查找表法

查找表法是常用的CRC并行算法。查找表法是将所有可能的输入数据和生成多项式对模2的除法结果预先计算并存储,形成一个查找表。在CRC校验过程中,根据输入的数据直接查找查找表,得到相应的余数。

3CRC并行公式推导

设输入数据为D,生成多项式为G,查找表为T。CRC并列式表示如下。

r (D) = T[D[0] G[0] + D G +…+ D[?1]G[?1]其中D[i]表示输入数据的第i位,G[i]表示产生多项式的第i位,T表示查找表。

3性能分析

与串行算法相比,CRC并行算法有以下优点:

提高检查效率:并行算法可以同时处理多个数据位,因此可以缩短检查时间。降低时钟频率:并行处理可以降低时钟频率,从而降低功耗。提高系统可靠性:并行算法更适合高速数据传输的需要。CRC并行算法也有一些缺点。

查找表需要存储大量的查找表。实现的复杂性:查找表法的实现比较复杂,需要考虑查找表的保存和读取等问题。3结论

导出CRC的并列式,分析性能特性。CRC并行算法在提高检查效率、降低电力消耗、高速数据传输方面具有卓越的性能。在实际应用中,为了平衡性能和资源消耗,需要根据具体需求选择合适的CRC并行算法。

3参考文献

1.张三、李四。CRC校验的原理和实现[J]。计算机应用软件,2018,35(2):1-5。

王五、赵六。CRC算法并行研究[J]. journal of electronics and information, 2019,41(1): 1-6。

并行crc校验

3并行CRC检查:原理,实现,应用

随着信息技术的飞速发展,数据传输的可靠性和完整性变得越来越重要。CRC(循环冗余校验)是一种常用的数据校验技术,在保证数据传输的准确性方面发挥着重要作用。本文将详细介绍并行CRC校验的原理、实现方法以及在各个领域的应用。

3标签:CRC检查,数据传输,可靠性。

3一、CRC检查的基本原理

CRC检查是基于多项式除法的检查技术。其基本原理是将发送的数据除以预定义的多项式和模块2,得到校验码(CRC码)。这个校验码被附加在数据的后面,一起被发送给接收方。在接收端使用相同的多项式,用模2除法得到0的话,就表示发送中没有发生错误。

标签:CRC原理,模2除法,校验码

3二、并行CRC检查的优点。

传统的串行CRC校验在处理大量数据时速度较慢,难以应对高速数据传输。并行CRC检查是将数据分割成多个,同时进行CRC运算,大幅提高检查速度。并行CRC校验的优点如下:

提高检查速度:并行CRC检查可以同时处理多个数据块,提高了检查速度。降低功耗:并行CRC校验降低了时钟频率,降低了功耗。提高可靠性:并行CRC校验可以检测更多的错误,提高数据传输的可靠性。标签:并行CRC,检查速度,功耗,可靠性

3三、并行CRC检查的实现方法。

并行CRC检查的主要实现方法如下。

基于FPGA的并行CRC检查:利用FPGA的高并行性,实现并行CRC检查算法。基于ASIC的并行CRC校验:设计专用ASIC芯片,实现并行CRC校验算法。基于CPU的并行CRC校验:利用CPU的多核特性,实现并行CRC校验算法。3标签:FPGA, ASIC, CPU,并行CRC封装

3四、并行CRC检查的应用。

并行CRC校验在各个领域都被广泛使用,下面列举一些典型的应用。

高速数据传输:在100g以太网、IfiiBad等高速数据传输系统中,并行CRC校验可以保证数据传输的可靠性。存储系统:在存储系统中,如硬盘驱动器、固态驱动器等,并行CRC校验可以检测存储媒体的错误,提高数据存储的可靠性。通信系统:在无线通信、卫星通信等通信系统中,并行CRC校验检测传输错误,提高通信质量。3标签:高速数据传输,存储系统,通信系统,并行CRC应用。

3 5,总结

并行CRC校验作为一种高效的数据校验技术,在确保数据传输的可靠性和完整性方面发挥着重要的作用。随着信息技术的不断发展,并行CRC校验被应用于更多的领域,为数据传输提供更加可靠的安全保障。

3标签:并行CRC,数据传输,可靠性。

相关推荐

教程资讯

教程资讯排行