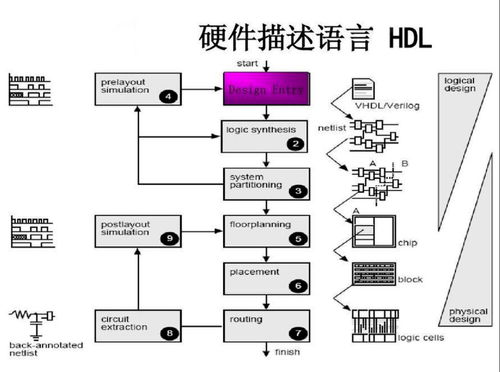

超高速硬件描述语言,VHDL与Verilog的崛起与挑战

时间:2024-10-07 来源:网络 人气:

超高速硬件描述语言:VHDL与Verilog的崛起与挑战

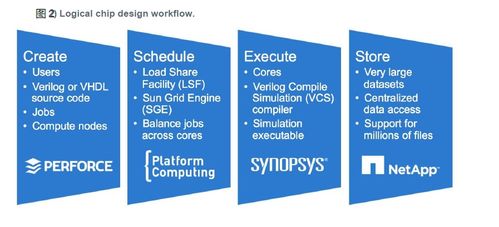

随着电子技术的飞速发展,集成电路(IC)的设计和制造技术也在不断进步。为了满足日益复杂和高速的电子系统需求,超高速硬件描述语言(VHDL和Verilog)应运而生。本文将探讨这两种语言的发展历程、特点以及它们在数字电路设计中的应用。

一、VHDL:超高速集成电路硬件描述语言

1.1 VHDL的起源与发展

VHDL(Very High Speed Integrated Circuit Hardware Description Language)全称为超高速集成电路硬件描述语言,起源于20世纪80年代初的美国国防部。当时,为了实现超高速集成电路(VHSIC)项目,美国国防部开发了VHDL语言。1987年,IEEE协会批准VHDL为IEEE工业标准,即IEEE 1076-1987。此后,VHDL得到了广泛的应用和推广。

1.2 VHDL的特点

(1)功能强大:VHDL具有丰富的数据类型、运算符和语句,能够描述复杂的数字电路。

(2)设计方式多样:VHDL支持自顶向下、自底向上和混合设计方法,适用于不同层次的设计。

(3)硬件描述能力:VHDL能够描述硬件电路的结构、行为和时序,为数字电路设计提供了强大的支持。

(4)移植能力强:VHDL设计描述与器件无关,便于在不同平台和设备上移植。

二、Verilog:硬件描述语言的新星

2.1 Verilog的起源与发展

Verilog(Hardware Description Language)是一种硬件描述语言,由Gateway Design Automation公司于1982年开发。后来,Cadence Design Systems公司收购了Gateway Design Automation,并最终将Verilog标准化为IEEE 1364。Verilog与VHDL类似,也是一种用于描述数字电路的语言。

2.2 Verilog的特点

(1)语法自由、易学易用:Verilog的语法类似于高级编程语言,易于学习和使用。

(2)支持算法级、门级设计:Verilog能够描述数字电路的算法级和门级设计,适用于不同层次的设计。

(3)代码简洁:Verilog的代码简洁明了,便于阅读和维护。

(4)发展迅速:Verilog在数字电路设计领域得到了广泛应用,发展迅速。

三、VHDL与Verilog的应用场景

3.1 VHDL的应用场景

(1)IC设计:VHDL在IC设计中具有广泛的应用,如数字信号处理器、FPGA/CPLD/EPLD等。

(2)嵌入式系统:VHDL在嵌入式系统设计中具有重要作用,如汽车电子、通信设备等。

(3)系统级仿真:VHDL在系统级仿真中具有优势,能够模拟整个系统的行为和性能。

3.2 Verilog的应用场景

(1)FPGA开发:Verilog在FPGA开发中具有广泛应用,如数字信号处理、通信系统等。

(2)ASIC设计:Verilog在ASIC设计中具有优势,能够描述复杂的数字电路。

(3)系统级仿真:Verilog在系统级仿真中具有广泛的应用,如汽车电子、通信设备等。

四、VHDL与Verilog的挑战与展望

4.1 挑战

(1)设计复杂度:随着数字电路的复杂度不断提高,VHDL和Verilog的设计难度也在增加。

(2)设计周期:VHDL和Verilog的设计周期较长,需要投入大量的人力和物力。

(3)跨平台兼容性:VHDL和Verilog在不同平台和设备上的兼容性有待提高。

4.2 展望

(1)设计自动化:随着设计自动化技术的发展,VHDL和Verilog的设计效率将得到提高。

(2)跨平台兼容性:随着跨平台兼容性的提高,VHDL和Verilog将在更多领域得到应用。

(3)人工智能:人工智能技术在VH

相关推荐

教程资讯

教程资讯排行