vhdl硬件描述语言,从入门到实践

时间:2024-10-05 来源:网络 人气:

深入浅出VHDL硬件描述语言:从入门到实践

随着电子技术的飞速发展,硬件描述语言(HDL)在数字电路设计领域扮演着越来越重要的角色。VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)作为一种广泛使用的HDL,具有强大的功能和灵活性。本文将带领读者从入门到实践,全面了解VHDL硬件描述语言。

什么是VHDL?

VHDL是一种用于描述、设计和验证数字电路的硬件描述语言。它由美国国防部在20世纪80年代初开发,旨在实现高速集成电路(VHSIC)项目。VHDL具有以下特点:

可描述性:VHDL可以描述从简单逻辑门到复杂数字系统的各种电路。

可验证性:VHDL支持仿真和验证,确保设计的正确性。

可移植性:VHDL与工艺无关,可以用于不同的半导体工艺。

可扩展性:VHDL支持层次化设计,方便模块化开发。

VHDL基础语法

VHDL的语法类似于高级编程语言,包括以下基本元素:

实体(Entity):定义模块的接口和功能。

架构(Architecture):描述模块的内部结构和行为。

信号(Signal):表示模块内部或模块之间的数据传输。

过程(Process):描述模块的行为,如组合逻辑和时序逻辑。

常量(Constant):表示固定值。

变量(Variable):表示可变值。

一个简单的VHDL设计实例

以下是一个简单的VHDL代码示例,实现一个2位全加器:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity full_adder is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

sum : out STD_LOGIC;

carry : out STD_LOGIC);

end full_adder;

architecture Behavioral of full_adder is

begin

process(a, b)

begin

if (a = '1' and b = '1') then

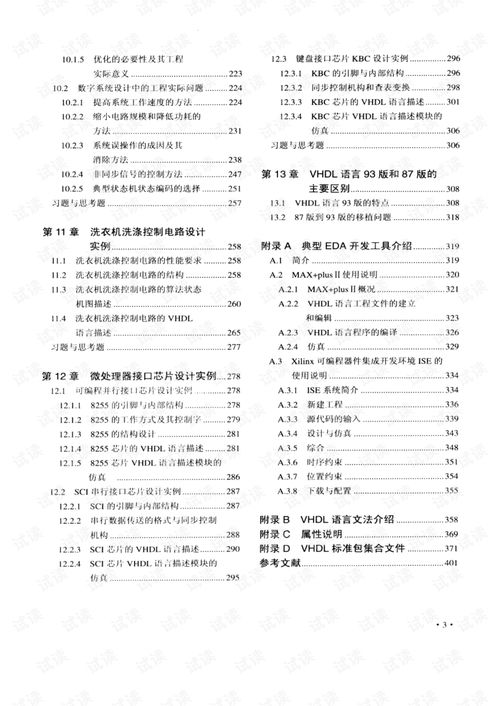

sum 仿真与综合

在VHDL设计中,仿真和综合是两个重要的步骤。

综合:将VHDL代码转换为硬件描述语言(如Verilog),以便在FPGA或ASIC上实现。

VHDL应用领域

VHDL在以下领域具有广泛的应用:

数字电路设计:VHDL可以用于设计各种数字电路,如逻辑门、计数器、微处理器等。

数字系统设计:VHDL可以用于设计复杂的数字系统,如通信系统、消费电子等。

嵌入式系统设计:VHDL可以用于设计嵌入式系统中的数字电路。

教学与科研:VHDL是数字电路设计的重要工具,广泛应用于教学和科研领域。

本文从VHDL的简介、基础语法、设计实例、仿真与综合、应用领域等方面,全面介绍了VHDL硬件描述语言。通过学习本文,读者可以掌握VHDL的基本知识和应用技巧,为数字电路设计打下坚实的基础。

相关推荐

教程资讯

教程资讯排行