verilog硬件描述语言,从入门到实践

时间:2024-10-01 来源:网络 人气:

深入浅出Verilog硬件描述语言:从入门到实践

在数字电路设计领域,硬件描述语言(HDL)是工程师们不可或缺的工具。Verilog HDL作为一种广泛使用的硬件描述语言,因其简洁的语法和强大的功能而受到工程师的青睐。本文将带领读者从Verilog的入门知识开始,逐步深入到其实践应用,帮助读者全面了解Verilog硬件描述语言。

一、Verilog简介

Verilog HDL,全称为Verilog Hardware Description Language,是一种用于描述数字电路硬件结构和行为的语言。它允许设计者以文本形式描述电子系统的行为和结构,从而实现数字电路的设计、仿真和综合。Verilog语言最初由Gateway Design Automation开发,后来被Cadence Design Systems收购,并最终成为了一个开放的标准,被IEEE标准化为IEEE 1364。

二、Verilog基本语法

Verilog的语法类似于C语言,但也有一些本质的区别。以下是一些Verilog的基本语法元素:

数据类型:Verilog支持多种数据类型,如reg、wire、integer等。

运算符:Verilog提供了丰富的运算符,包括算术运算符、逻辑运算符、关系运算符等。

模块:Verilog中的模块是设计的基本单元,用于描述电路的功能。

端口:模块的端口用于与其他模块进行交互。

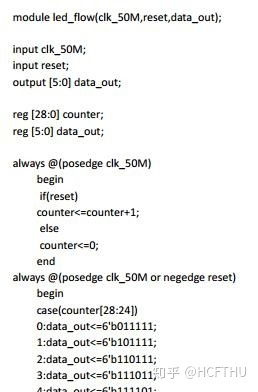

三、Verilog模块与端口

模块是Verilog设计的基本单元,用于描述电路的功能。一个模块通常包含以下部分:

模块名:用于标识模块的唯一名称。

端口列表:定义模块的输入和输出端口。

内部信号:用于在模块内部进行数据传输。

行为描述:描述模块的功能。

端口是模块与外部世界交互的接口,分为输入端口和输出端口。输入端口用于接收外部信号,输出端口用于向外部发送信号。

四、组合逻辑与时序逻辑

Verilog中的逻辑可以分为组合逻辑和时序逻辑两种类型。

组合逻辑:组合逻辑的输出仅取决于当前输入,与历史输入无关。组合逻辑通常用于实现逻辑门、算术运算器等。

时序逻辑:时序逻辑的输出不仅取决于当前输入,还取决于历史输入。时序逻辑通常用于实现计数器、状态机等。

在Verilog中,组合逻辑和时序逻辑可以通过always块进行描述。

五、时钟域与同步设计

在数字电路设计中,时钟域和同步设计是非常重要的概念。时钟域是指电路中所有模块共享的时钟信号,同步设计是指电路中的所有操作都在时钟信号的上升沿或下降沿进行。

在Verilog中,时钟域可以通过时钟生成模块进行描述,同步设计可以通过always块中的时钟敏感语句进行实现。

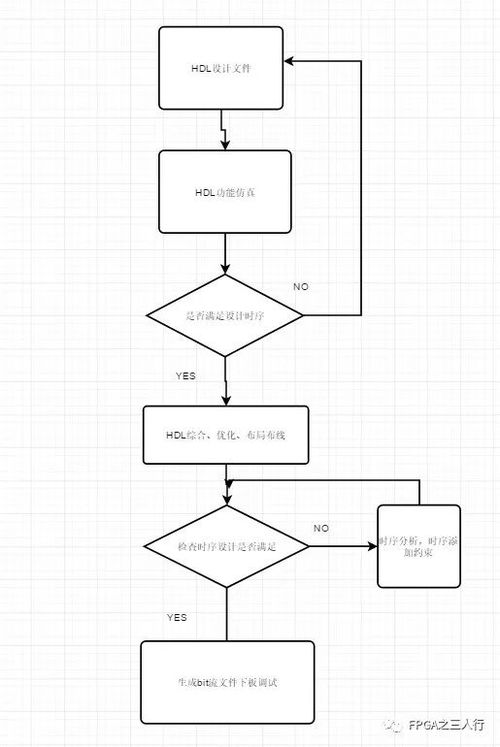

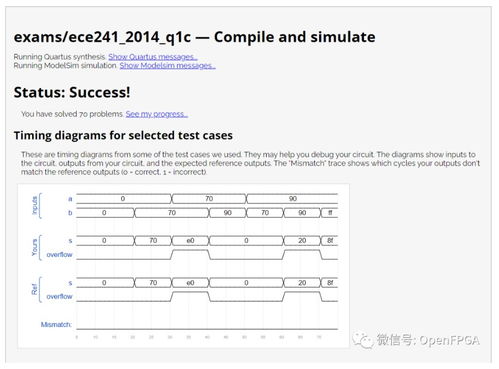

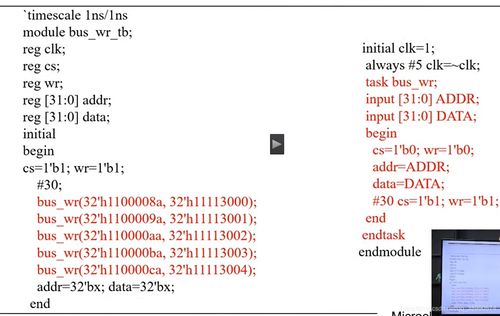

六、测试与仿真

在Verilog设计中,测试和仿真是非常重要的环节。测试用于验证设计的正确性,仿真用于模拟电路的行为。

七、Verilog高级特性

Verilog除了基本语法和功能外,还提供了一些高级特性,如任务、函数、多维数组、结构体和系统函数等。

这些高级特性可以用于提高设计的可读性和可维护性,使设计更加灵活和高效。

Verilog

相关推荐

教程资讯

教程资讯排行